───────────────────────────────────

<更新情報>

2019.01.10

・「1.3 送端終端」で、配線長の説明に誤りがあり訂正。

2018.07.12

・送端終端の配線長の制限について説明を追加

───────────────────────────────────

はじめに

ここでは、伝送路(伝送線路、Transmission line)の終端と信号波形との関係について説明します。

その話の前にまず、基本的ですが重要なことを整理しておきます。

伝送路を一言で簡単に表現すると、時間の要素が関係する回路です。信号が伝わるまで時間がかかるという意味ですが、時間の要素を考えなくてはいけません。伝送路は具体的には、無線通信機器などの高周波を扱う回路や高速の信号(立ち上がり時間の短い)を扱う回路では必須です。

電気信号がA点からB点まで伝わるときほとんど一瞬に伝わるように思えますが、このわずかな時間を無視できない回路です。信号波形を考えるとき、避けては通れません。

集中定数回路(Lumped Constant Circuit)はこれと対比し、信号が伝わるまでの時間を気にする必要がありません。正しく表現すると、時間の要素を無視できる回路のことです。周波数の低い、たとえばオーディオ(可聴帯域)周波数の回路は、一般にこれに該当します。このような回路では、電気信号の伝わる時間は無視して考えることができます。

-

もう使われなくなったと書いて問題ないはずですが、電話の伝送線はたかだか3KHzまでの低周波回路にも関わらず、長距離では終端した伝送路が必要です。配線長が長大で低周波でも波長との関係を無視できないからです。言い換えると、波長との関係を無視できない回路はすべて伝送路で扱うことが必要です。

3KHzの電気信号の波長は、波長短縮率を無視すると100キロメートルです。波長の数倍の距離を伝送するときは、伝送路により伝えなければ信号は乱れます。昔の長距離電話のラインはこれより長いところがあり伝送路は必須でした。(信号は減衰するので、途中に増幅器を入れて中継することもある。)

現在は、電話の幹線はすべて光ファイバーのディジタル回線で、残るのはユーザー宅と電話局の間のみです。

伝送路を終端(termination)する方法は種類があります。いくつかの方法について、回路シミュレータの動作結果と共に、なぜそのように動作するのかを説明します。

回路シミュレータは便利な道具には違いないのですが、回路がなぜそのように動くのか理屈がわかっていないと思うように使いこなすことはできません。どんな理屈で動くのか、理解するための手助けになれば幸いです。

信号が

信号と波長

「伝送路の仕組み[1]ー 距離と形状」にも書いたように、伝送路の物理的な長さと波長の関係で、ある一定の長さを超える条件では、信号の波長を無視して扱うことができません。

これが何を意味するのか?

何も考えずに単純に線でつなぐだけでは信号を正しく伝えることができないのです。

具体的には、伝送路の長さが伝播遅延時間 (propagation delay time)の2.5倍(*1)を超えるあたりから、伝送路の特性を無視した接続方法では信号に悪い影響が顕著に現れ始め、長くなるほど伝えたい信号はまったく伝わらなくなります。

-

伝送路の長さが影響を及ぼす伝播時間との比率については、文献によりさまざまです。これよりはるかに厳しい条件のものもあります。どれが正しくどれが正しくないという問題ではないのです。

問題の本質は、何倍以内なら無視できるかということではなく、信号に対してどの程度の影響が現れるのかです。何倍以内なら無視できると単純に言えません。条件により変化するからです。必要なら波形にどの程度の影響があるのか計算で求める方法もあります。すべての信号はアナログであると主張する理由です。

ディジタル処理はアナログ信号を、さも1と0であるかのようにみなしているに過ぎません。ノイズがしきい値を超えるか超えないかで、1と0は反転します。たとえばA/D変換器の上位ビットなら、変換後の信号には原信号には無い大きなノイズが発生します。ディジタルテレビ放送に変わってから、ごくまれに見苦しい画面が出ることがありますが、似たような原因による顕著な例です。

伝送路の遅延時間が信号の立ち上がり時間の2.5倍程度より長い条件では、回路は適切な終端をしないと、信号は正しく伝わりません。

前置きはこれくらいにして終端の具体的な方法について説明します。

1 終端の方法

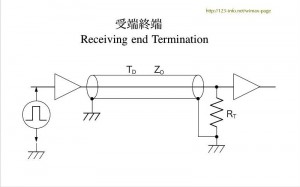

1.1 受端終端 Receiving end Termination

受信端で終端する方法です。別名は、並列終端 (Parallel termination)です。伝送路と負荷が並列になることからこのように呼びます。

技術的には、この方法は受信端の反射を 0にする(理想的な場合)ものです。(*2)

受端終端はごく普通で、「終端」という場合は、この方法を指すことが多いでしょう。1本の抵抗器でグランド(0ボルト=回路の基準電位)へ終端するものが標準的です。

| 図1.1 受端終端 | ||

|

反射を最小限にするにはRTはZOと等しい値を選びます。 |

特徴は、レシーバが(受信端で分圧しない場合は)ドライバの信号振幅を最大限に利用できる点です。後に出てくる送端終端との大きな違いは、終端抵抗が直流電力を消費することです。

方式とは無関係に、回路図には普通は現れないことですが、受信側には容量成分 (capacitance)がありますから、交流成分(信号が遷移する瞬間に流れる)の電力を消費します。

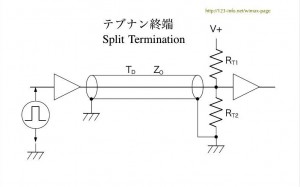

1.2 テブナン終端 Split Termination

「テブナンの定理」で有名なフランスの技術者の名前から来たものです(「テブナン終端」の名称は日本以外で通じるかどうかは知りません。)が、2本の合成抵抗で終端することにより1本の場合より少ない電流で駆動できる特徴があります。駆動能力の十分でないロジックICなどでは有効な方法です。

ロジックHIのときはドライバからRT2へ電流が流れ、ロジックLOのときはV+からRT1の方向へ流れてドライバが電流を吸い込みます。RT1とRT2の合成抵抗はZOと等しく、抵抗1本のときより電流が少ないことは直感的にお分かりでしょう。

ただし、この方式はロジック信号のときのみ使用できる方法であり、アナログ信号の終端には使えません。

| 図1.2 テブナン終端 | ||

|

受信端(並列)終端より少ない電流ですむ方法です。 |

-

一般にはあまり聞いたことが無いかもしれませんが、半導体テスタ(ハンディタイプのテスタ=マルチメータのことではなく、大がかりで複雑な装置です。)に使用するピンドライバ(pin driver)の中身はアナログ回路です。一般のICはロジックHIとLOの仕様(例 出力ピンでは出力電流と電圧)を規定しますが、ピンドライバは特性が仕様を満足するかどうか試験する信号を与える回路で、ロジックHIとLOの信号レベルを正確にプログラムできます。これを実現するには、ロジックICの構成で作ることはまず無理で、HIとLOの値を正確に出力(または入力)する機能をアナログ回路で構成して実現します。

信号を受ける側はアナログ・コンパレータです。用途により超高速(短い時間)で応答するものを使います。現在の市販のICには300ps程度で応答するものがあります。(精密でなおかつ早いほど安定して性能を出すことは等比級数的に難しくなります。)

このような回路では、テブナン終端のような方式は使用できませんが、ディジタルだのアナログだのという議論は無意味なのです。この領域ではディジタルもアナログもなく物理的な信号そのものです・

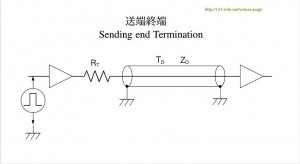

1.3 送端終端 Sending end Termination

終端抵抗を伝送路と直列に入れる方法で、別名は直列終端(series termination)やsource terminationです。

技術的には、この方法は送信端の反射を0にする(理想的な場合)ものです。(*2)

特徴は、直流電流が流れないことです。この方式はかなり変わった別の特徴があり、受信端の信号の反射により目的の波形を保ちます。シミュレーションの波形を見るとわかります。

送端終端は受信端の信号の反射により目的の波形を保つことから、配線長の制限があります。

配線長Lは信号が伝わる遅延時間が定まりますが、信号のサイクル時間(周期)よりも短くできない点です。

例をあげると、信号の基本周波数が100MHzのとき、サイクル時間(周期)は10nsですから、配線長による伝播遅延時間 (propagation delay time) は10nsよりも短くなければなりません。

つまり、信号の周期はこれより短くなくてはならないことから、逆に配線長はこれよりも短い条件では波形が乱れ保てなくなります。波長短縮率を60%を仮定すると、次の計算から配線長 Lは1.8メートル以内であることより長いことです。(訂正済み)

L \ge 300,000,000(m) \times 10ns \times 0.6

L \ge 1.8(m)

送端終端は、やはり駆動能力の十分でないICなどでは有効な方法です。

注意しなければならないのは、伝送路の途中の信号は反射波が見えますが、この事を知らずに伝送路の途中から信号を取り出したり、オシロスコープでこの波形(次の記事です)を見て慌てないことです。

直列終端について解説した資料などがたくさんあるようですが、この重要で基本的なことに触れないものが多く見られます。並列終端とは何がどう違うのかはじめは分からないと思います。

また、当然のことですが、受信端にZOと等しい抵抗をつけると、それはもはや直列終端ではない、単に抵抗で分割した並列終端回路に変わります。

| 図1.3 送端終端 | ||

|

直流電流が流れず、反射波により波形を整形します。 |

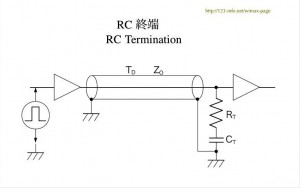

1.4 RC終端 RC Termination

特徴は、終端素子に直流電流が流れないことです。やはり駆動能力の十分でないICなどでは有効な方法です。

| 図1.4 RC終端 | ||

|

定常状態(直流)ではキャパシタには電流は流れませんが、信号レベルが遷移するときには導通します。時定数(=RT x CT)はクロックレートより十分に大きな値を選びます。デューティ比 (duty cycle)が50%に近い条件を維持できる場合は、直流的に平衡な状態にすることができこの回路はうまく働きます。

この条件では、終端抵抗の消費電力をテブナン終端よりも少ない値にすることができる特徴があります。(*2)

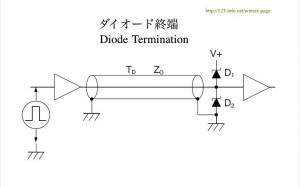

1.5 ダイオード終端 Diode Termination

実際にはショットキーダイオード (schottkey barrier diode)を使います。スイッチング特性の十分なものでないとこの用途には使えません。

ダイオードの働きは信号振幅を次の範囲内に抑えることです。

信号がロジックHIのときは、最大でV+とダイオードの順方向電圧 (VF: forward voltage)を足し算した値です。(ショットキーダイオードは0.3V程度)信号がロジックLOのときは、0VからダイオードのVFを引き算した値、約-0.3Vの範囲です。

ダイオードは2本しか端子がなく単純で簡単そうに見えますが、大間違いです。使いこなすのはなかなか手ごわい素子で、不適切な使用例が見られます。情報もあまり十分ではないように思います。この使用例ではない別の用途ですが、メーカーの情報でも中には誤解を招くような表現が見られます。

| 図1.5 ダイオード終端 | ||

|

最大でV+[VF]V〜-[VF]Vの範囲内に電圧を抑えます。 |

1.6 アクティブ終端 Active Termination

アクティブ終端 (active termination)は、抵抗器などの受動部品 (passive device)ではなく、能動部品 (active device)を使用する方法です。終端抵抗にFET (Field Effect Transistor) を使う方法や、複数の終端抵抗をトランジスタ・スイッチで切り替えるものがあります。

FETのドレイン電極(drain)とソース電極(source)の間をチャンネル(channel)と言いますが、この2つの電極の間はゲート(gate)電極の電圧により抵抗値を可変できる性質があります。この特性はBJT: バイポーラ・トランジスタ(Bipolar Junction Transistor) ではまねすることができません。BJTは、電流をオン・オフする用途には最適です。BJTで複数の終端抵抗を切り替えるものや、FETの性質を利用した終端抵抗の値を可変にするものがあります。

- 参考資料

-

*1

原著 Circuits, Interconnections, and Packaging for VLSI by H. B. Bakoglu IBM Thomas J. Watson Research Center 1990 Addison-Wesley

翻訳版 VLSIシステム設計 回路と実装の基礎 丸善(株)*2

High Speed Digital Design A Handbook of Black Magic

H. W. Jhonson, M. Graham Prentice-hall 1993